| 电源的发展必然需要小体积高效率产品,提高工作频率是必然趋势功率密度上看GaN, SiC占优势。传统硅材料在电源转换上应用发展几十年了,现已到达它的物理极限,发展空间有限。氮化镓材料最早是从LED及RF方面进入人们的视线,现在发展进入功率器件应用领域。适合高频高压。氮化镓GaN将提供高性能,低成本的方案。因氮化镓基于硅衬底,将来8,12英寸的晶元将大大降低使用成本。 常见功率器件:

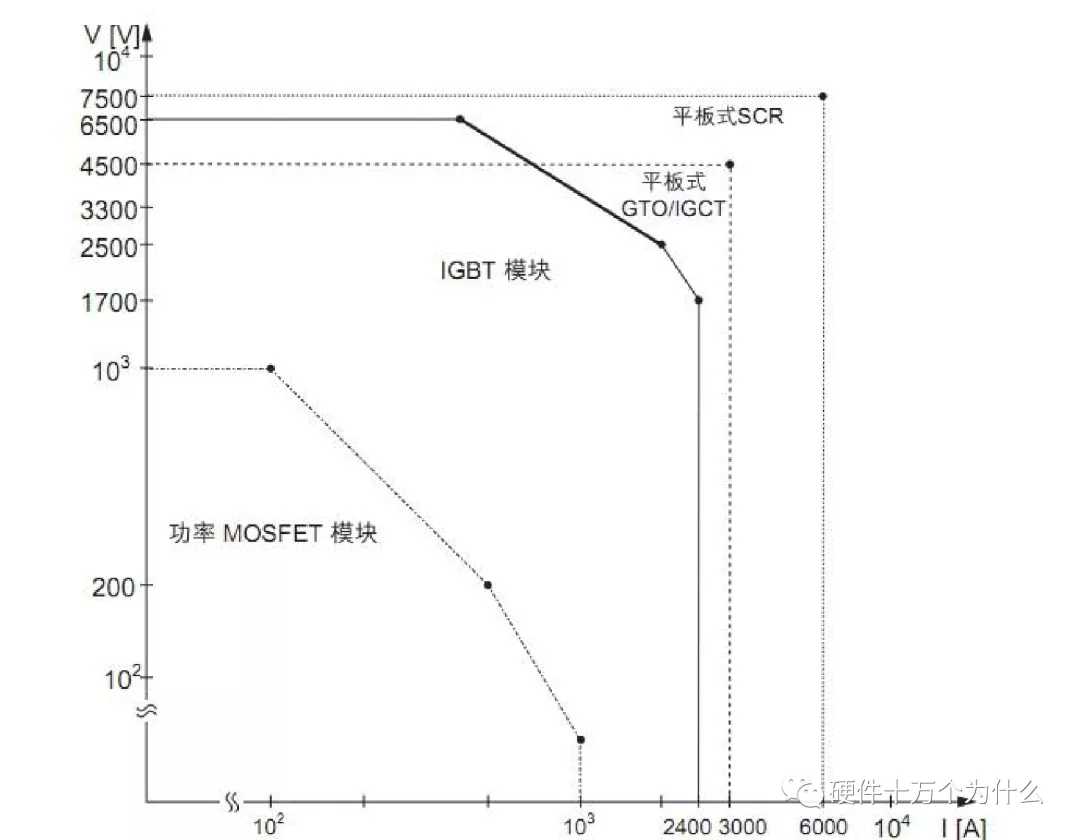

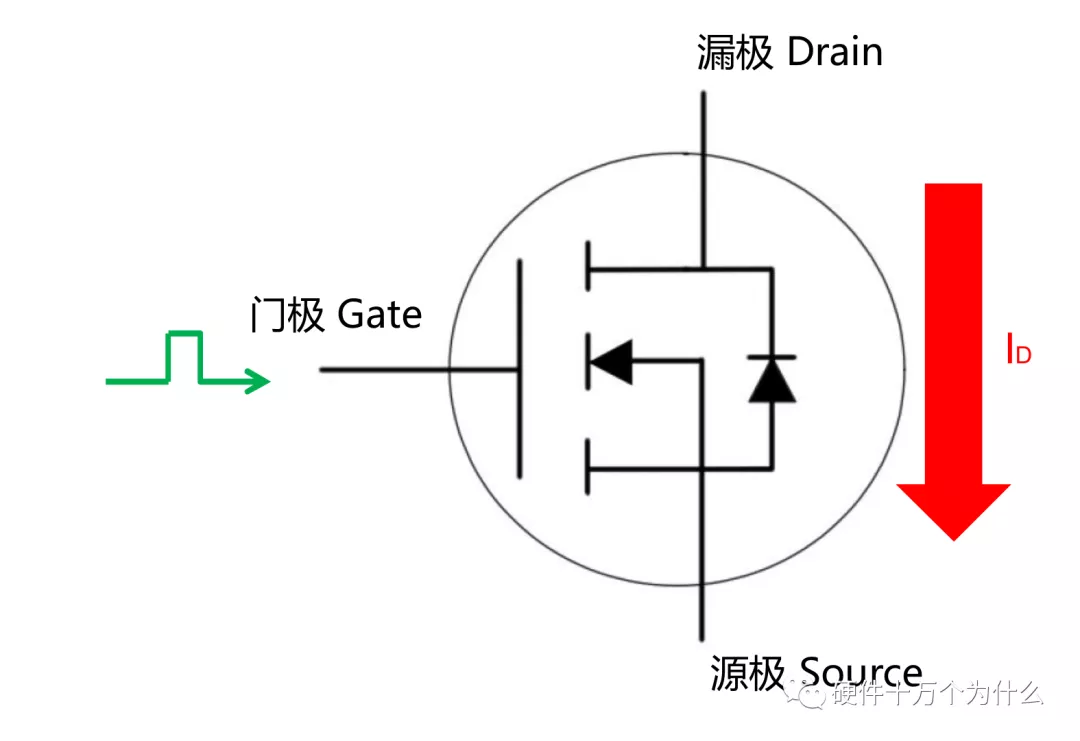

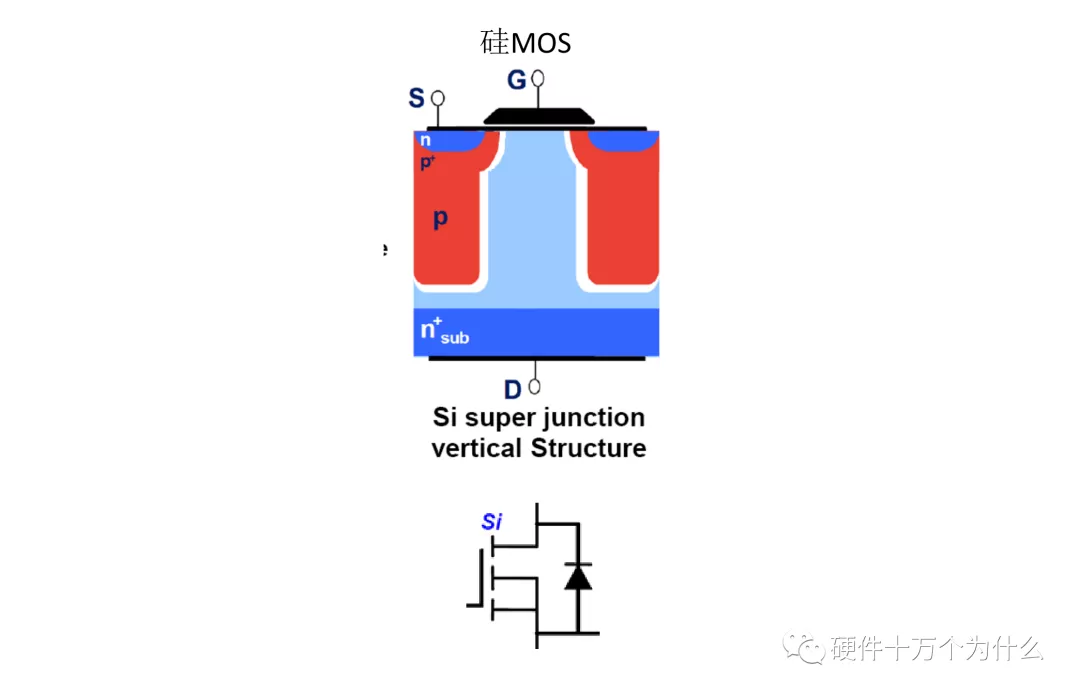

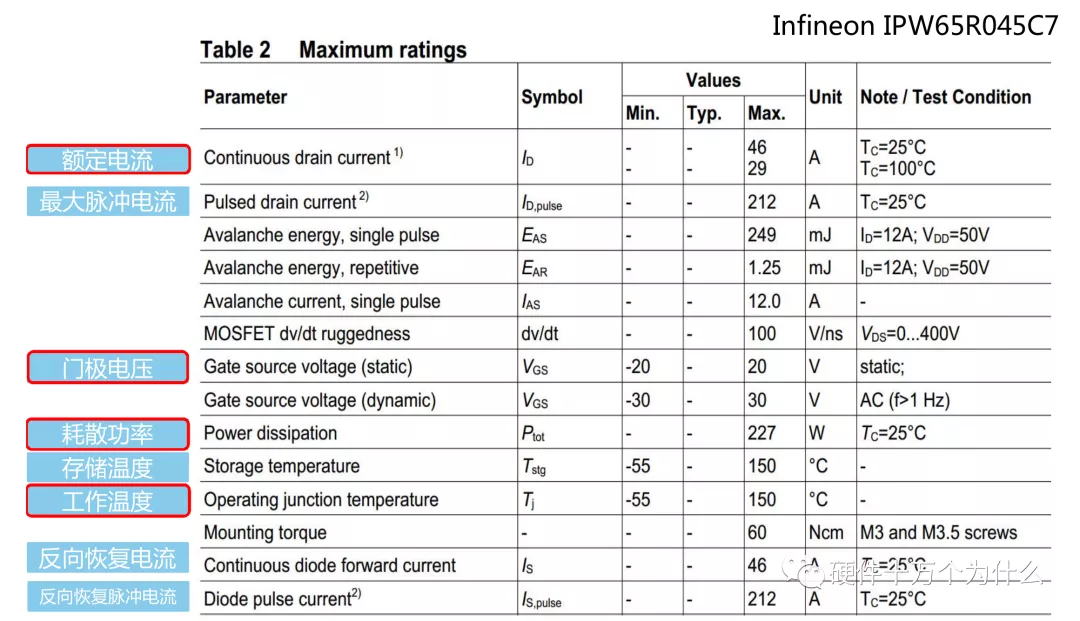

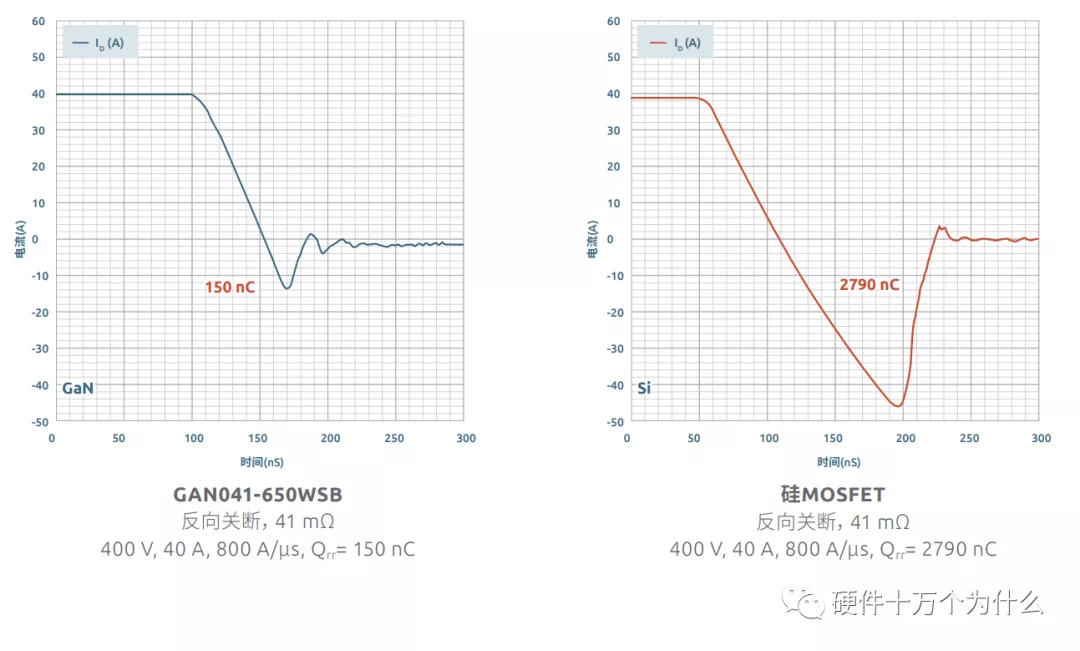

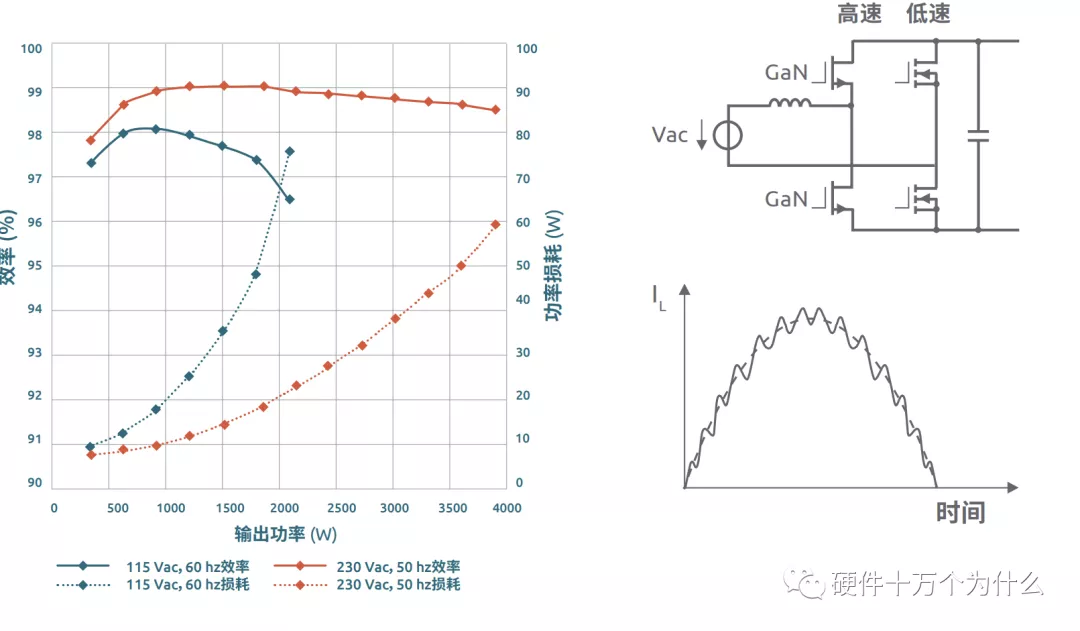

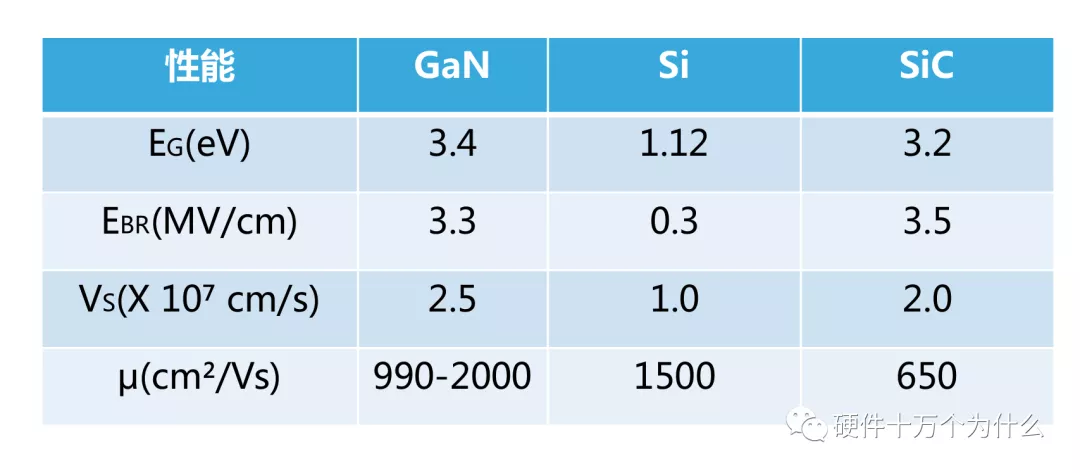

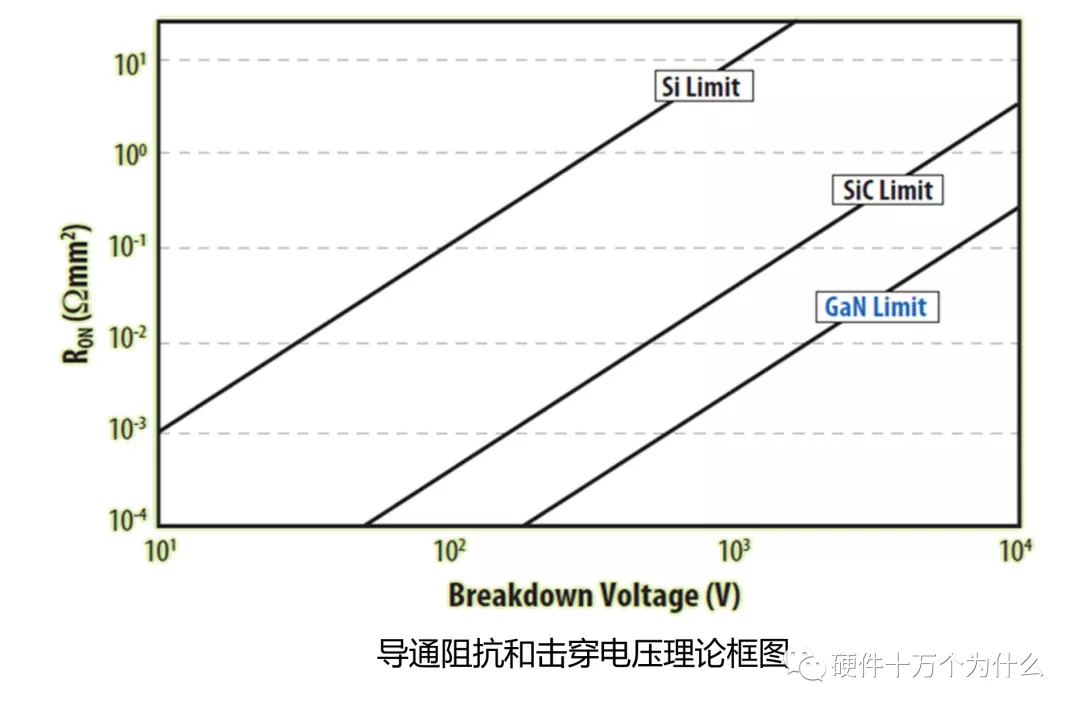

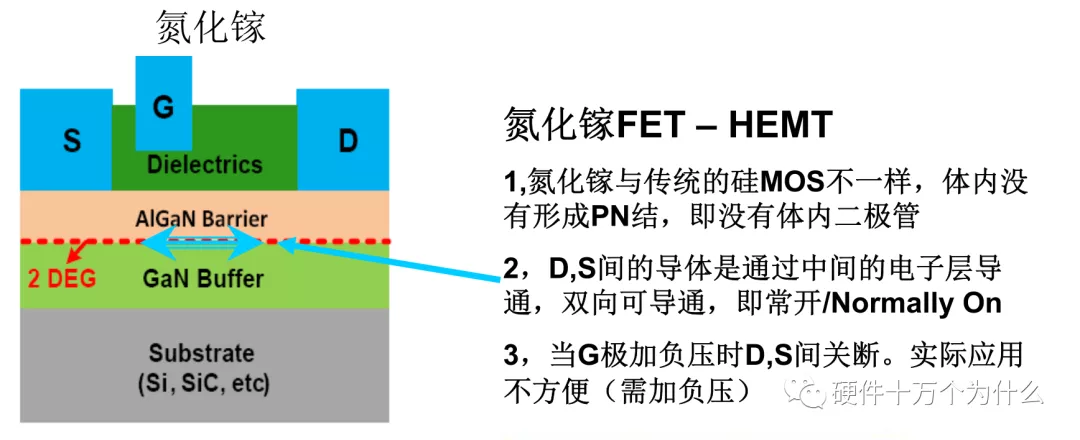

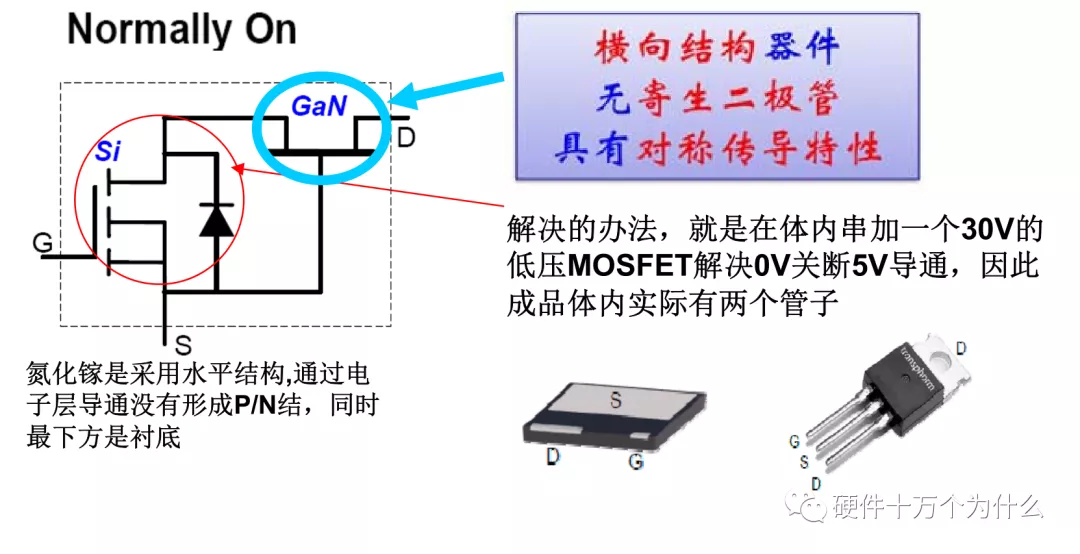

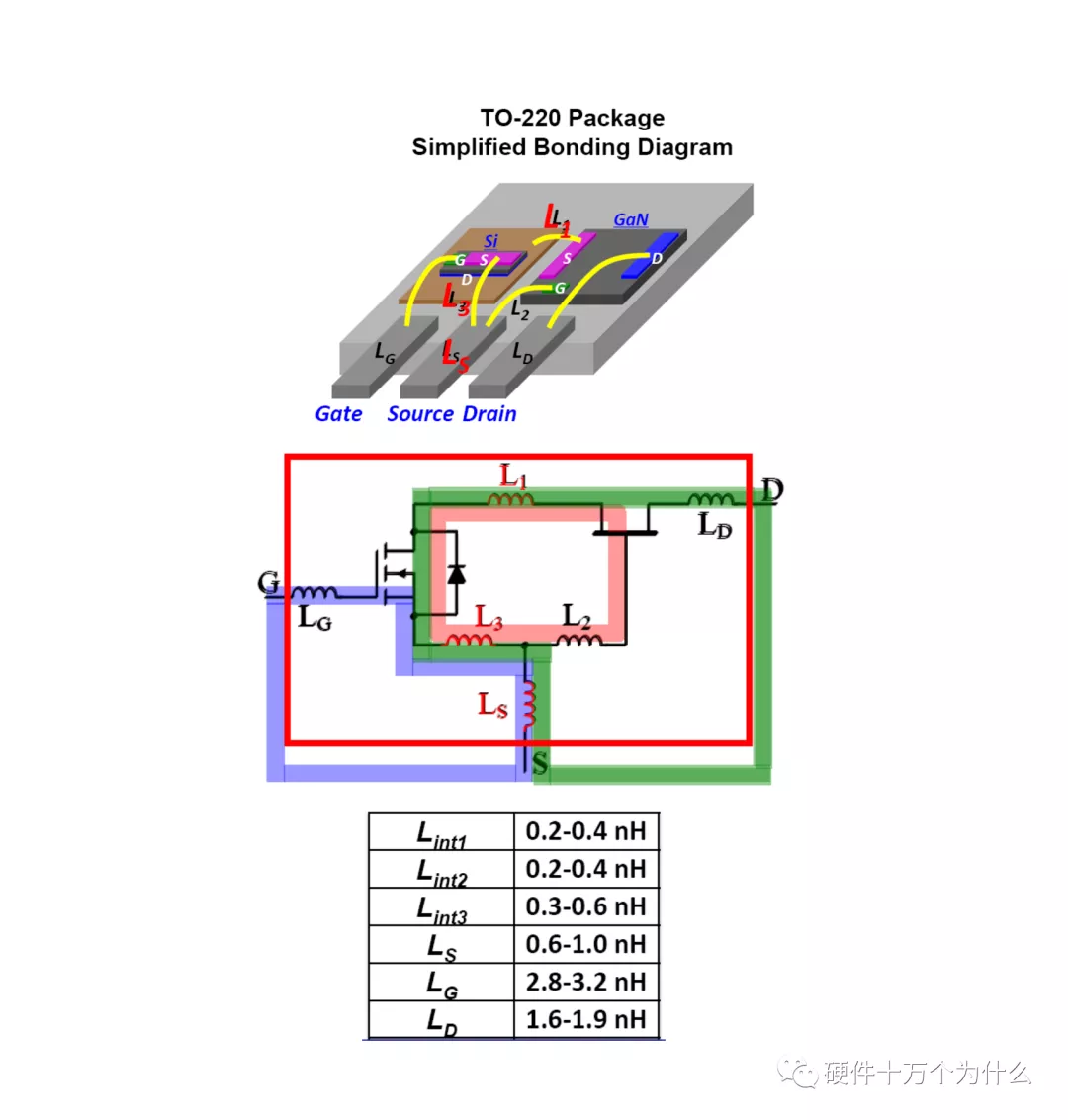

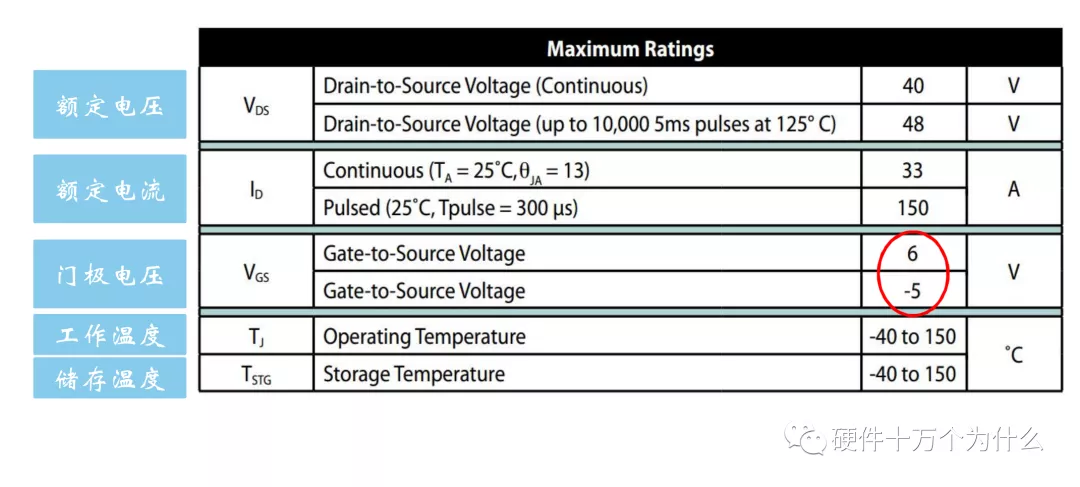

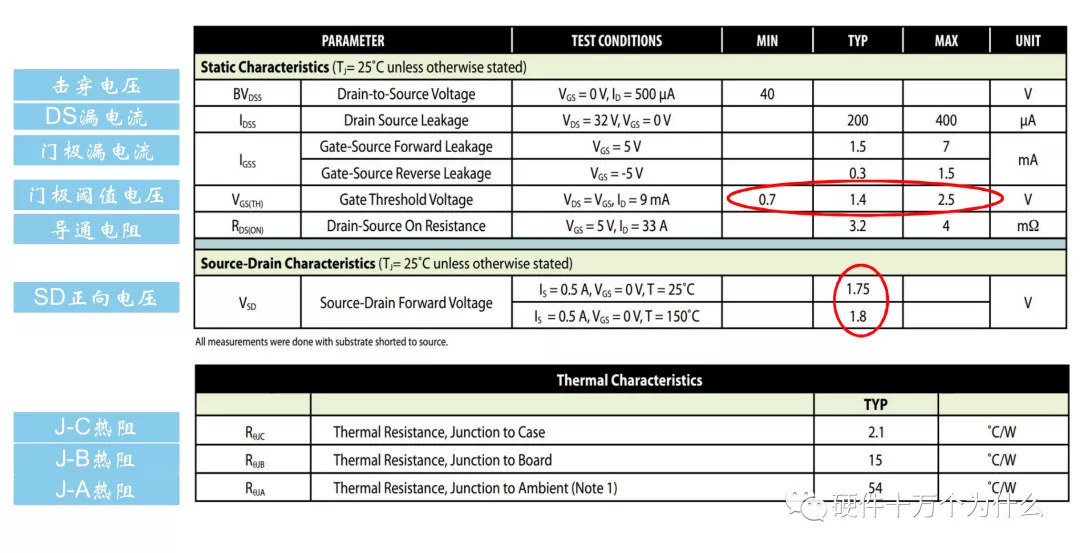

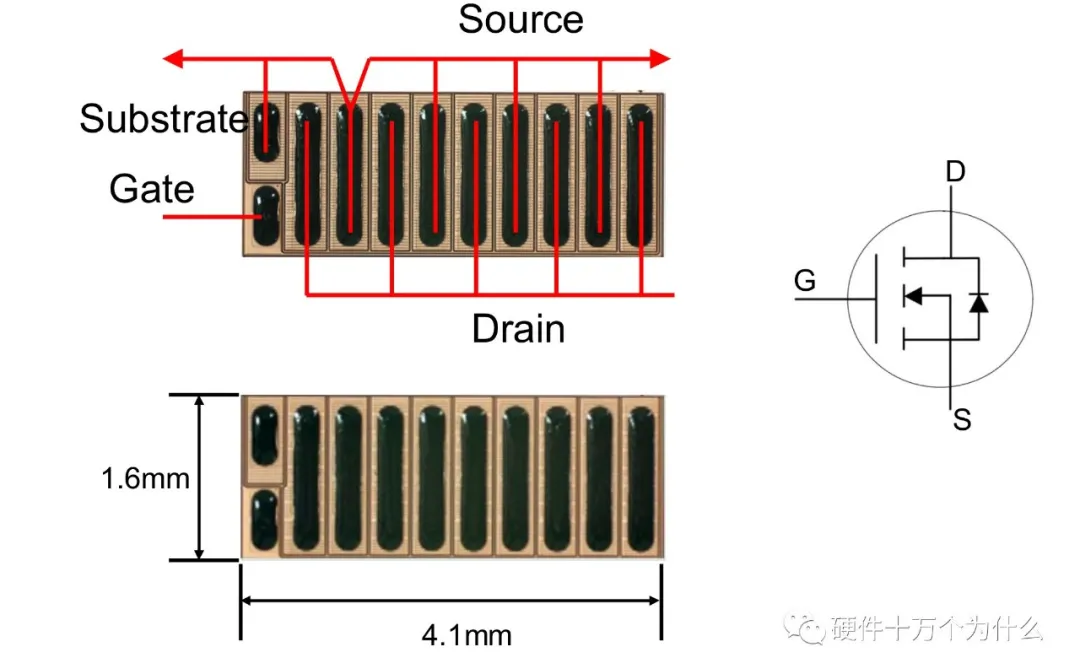

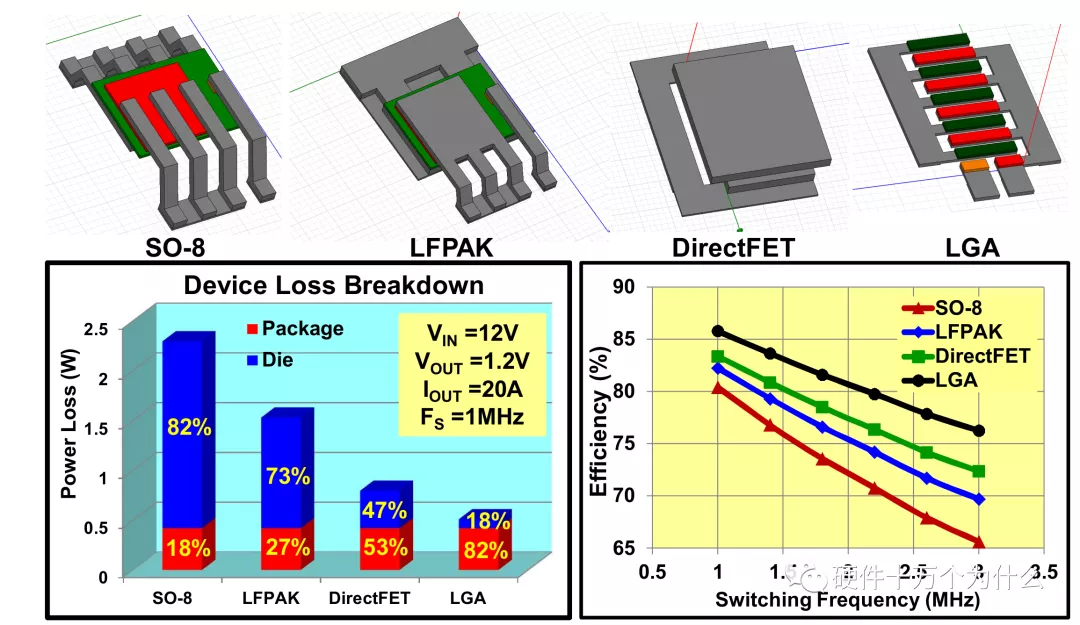

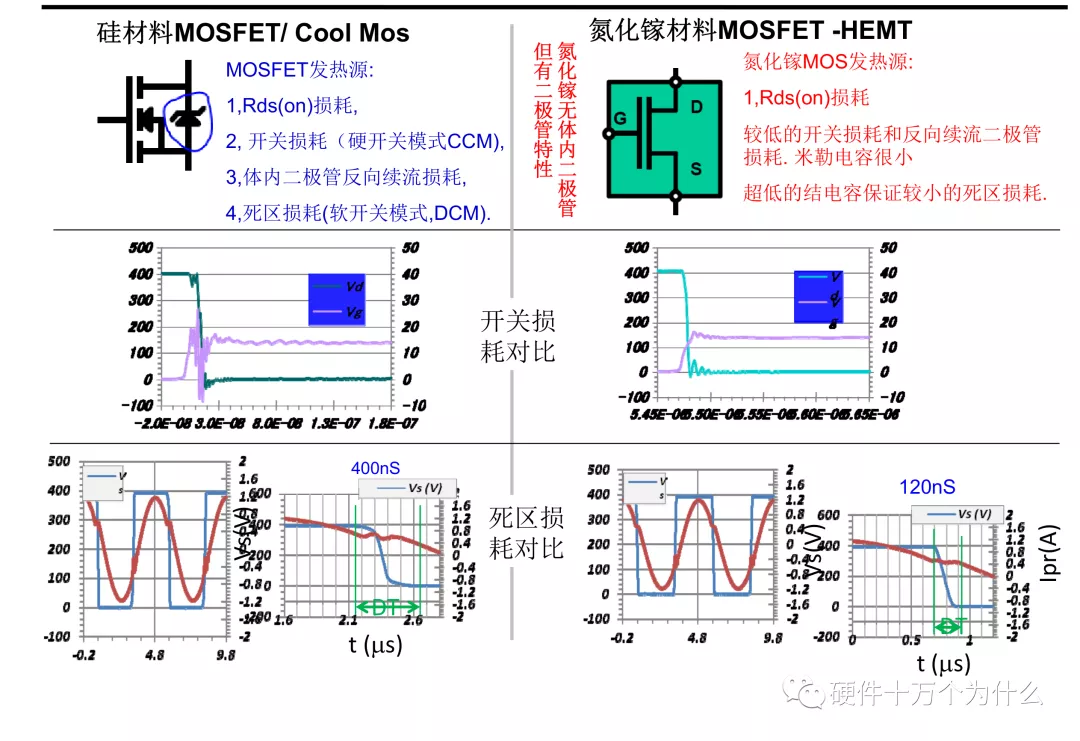

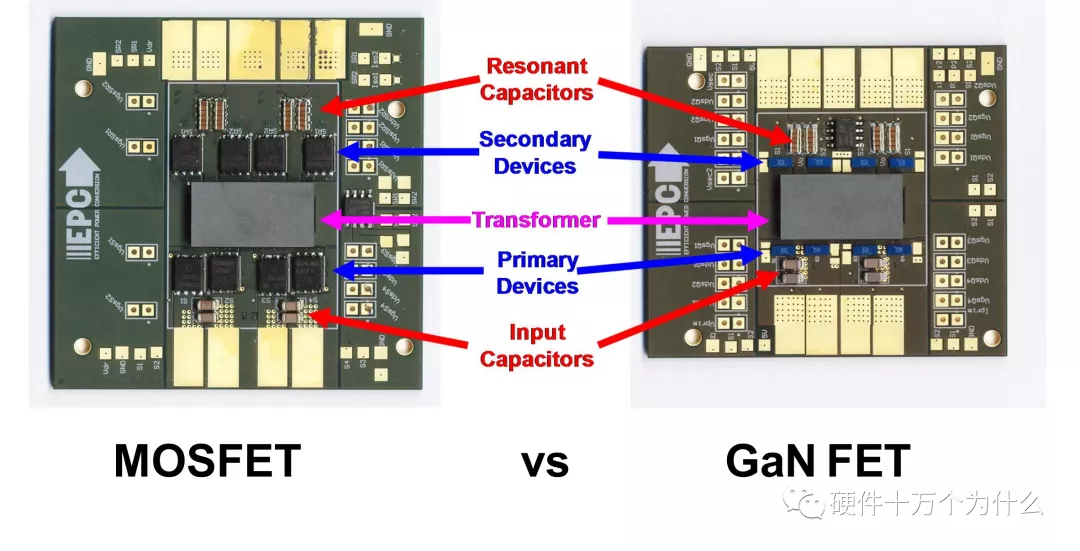

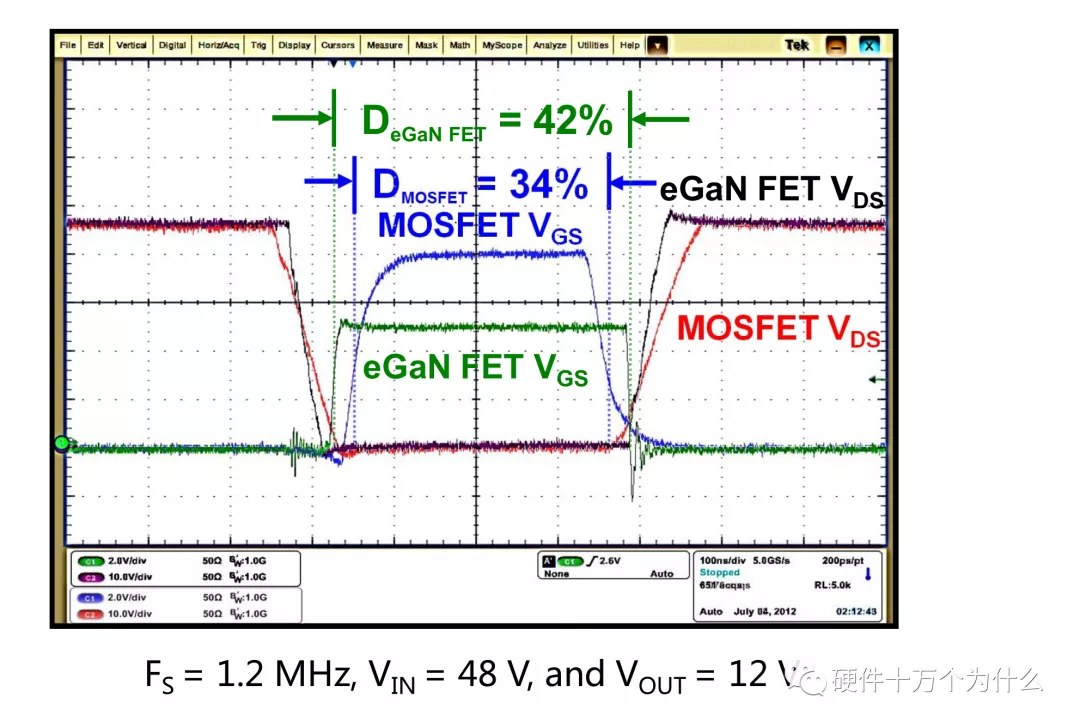

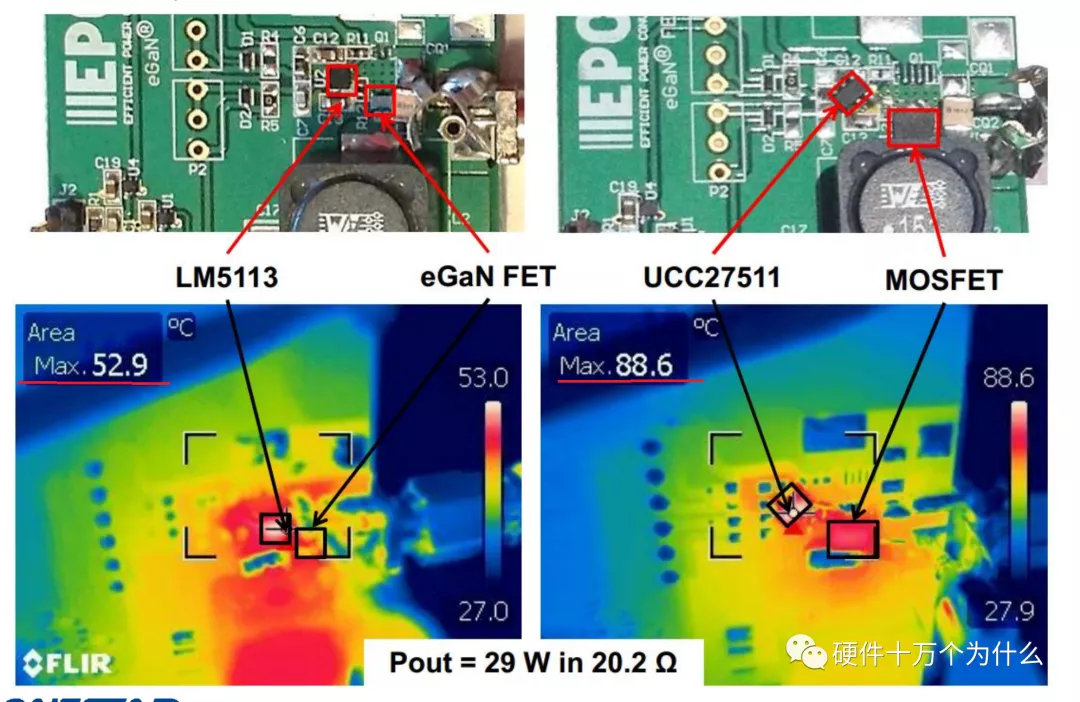

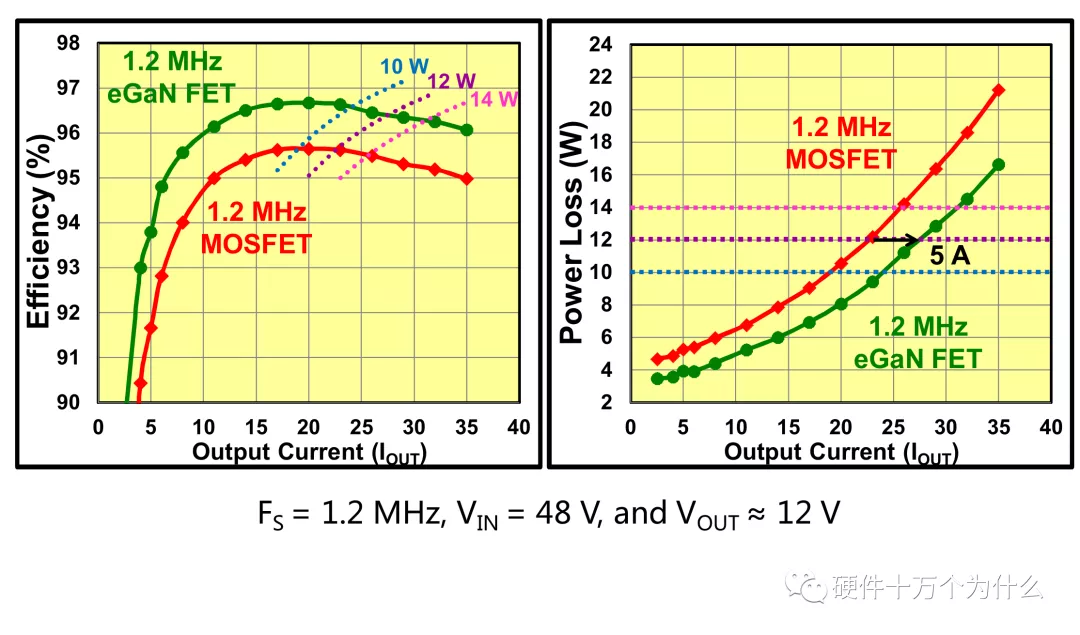

常见功率器件的功率范围:  MOSFET内部结构   硅材料的垂直结构使得P/N结存在,即必然有慢速的寄生二极管。 MOSFET主要参数表:  为什么需要GaN  •在相同的测试电路中,与硅器件相比,反向恢复损耗低。 •低导通阻抗 •更快速 •低分布电容 •小体积 •低成本 用GaN材料制成的功率器件GaN FET具有低的击穿电压、低的阈值电压、低的栅极电荷Qg,其开关频率高,导通电阻小。GaN FET优越的特性与其器件结构有极大的关系。但是它的缺点也不可忽视,在高频应用场合表现极为明显,比如其对寄生参数极其敏感,高频使用时极易使栅极电压产生振荡,引起栅极过电压,导致器件工作不稳定,甚至不安全。因此相较于传统的Si基半导体器件的驱动电路,GaN FET的驱动要求更为严苛。GaN FET的进步、应用的发展与其器件结构和驱动电路有密不可分的联系,因此,其器件结构和驱动电路的研究很有意义。 功率氮化镓场效应晶体管具备极低的Qrr和非常快速的开关转换,可减少开关损耗,实现最 高效率。包含半桥电路的方案,无论是AC/DC、DC/DC还是多相DC/AC逆变器,都能受益于 氮化镓场效应晶体管的应用。 如下图,GaN FET实现电源电路,效率更高,损耗更低。 氮化镓场效应晶体管图腾柱无桥PFC 在硬开关应用中,功率氮化镓场效应晶体管明显优于所有其他功率器件,当使用图腾柱 拓扑时,不但提高了性能,而且减少了50%器件数量。较少的器件数量可以降低系统成本, 提高功率密度,同时提升整个系统的可靠性。提高了整个系统的效率,也有助于减少昂贵 的散热冷却系统和在密闭环境中的相关操作成本。   导通阻抗和击穿电压的极限  氮化镓FET内部结构  GaN FET的器件结构及工作原理 GaN FET器件的结构目前主要有耗尽型(Depletion mode,D-mode)和增强型(Enhancement mode,E-mode)。增强型GaN FET又分单体GaN和Cascade GaN(共栅共源)。 1、耗尽型GaN FET 耗尽型GaN FET的器件结构如图所示。 耗尽型GaN FET采用Si材料作为GaN FET的基片,在Si基片基础上生长出高阻性的GaN晶体层,即氮化镓通道层(GaN channel)。一般在GaN层和Si衬底层之间添加氮化铝(AIN)绝缘层作为氮化镓缓冲层(GaN buffer),将器件和衬底隔离开来。AlGaN层存在GaN层和栅极(G)、源极(S)和漏极(D)之间;AlGaN层和GaN层之间可以产生具有高电子迁移率、低电阻特性的二维电子气(Two-Dimensional Electron Gas,2DEG),且它的浓度随AlGaN厚度先线性增加,然后达到饱和。 与Si传统器件不同,耗尽型GaN FET由于氮化物极强的极化效应,AlGaN/GaN异质结可以通过自发极化和压电极化效应在其界面形成很高浓度2DEG导电沟道,在零栅压下,器件处于导通状态。因此往往需要负压关断。耗尽型GaN FET不同于Si MOSFET的是,由于其栅极下方不存在与S极连接的P型寄生双极性区,因此没有寄生体二极管,故而器件开关损耗小、具有对称的传导特性。因此GaN FET可由正栅源电压VGS或正栅漏电压VGD驱动。 2、增强型GaN FET 对于耗尽型GaN FET,要关断器件,必须加负栅压。这意味着电路中一旦有耗尽型GaN FET,就会增加栅极驱动设计的复杂性,而且易发生误导通,有直通的潜在威胁,使电路稳定性和安全性降低。增强型GaN FET则相反,只有加正偏压才会导通,减小了电路复杂性,稳定性和安全性也较好。目前,增强型GaN FET主要是在耗尽型高电子迁移率晶体管(Gallium Nitride High Electron Mobility Transistor,GaN HEMT)结构的基础上改进而成。目前主要的增强型GaN FET结构方案包括:P型栅、凹槽栅、Cascode结构等。 3、 P型栅结构 有很多学者研究P型栅结构的GaN FET,如图所示。与耗尽型不同的是,P型栅结构是在AlGaN势垒层上生长了一个带正电的P型GaN栅极,如图中的P-GaN层。P型GaN层可以拉升AlGaN势垒层的能带,起到耗尽2DEG的作用,以实现常断特性。当施加足够的正VGS时,使栅源电压大于阈值电压,P-GaN层的内电场被削弱,2DEG浓度上升,形成导通沟道,GaN FET器件导通。随着VGS的降低且小于阈值电压,沟道又逐渐关闭,GaNFET器件关断。因此,这种结构主要是通过控制P型栅极势垒的电位,升降AlGaN势垒层的能带,使2DEG的浓度改变来实现对GaNFET器件的通断控制。 在P型栅结构的基础上,采用在P-GaN层上沉积TiN金属,形成三层掩膜的栅极结构,从而实现肖特基接触,如图所示。这种结构存在栅极场板,可增加高压应用场板设计的灵活性。实验证明,这种结构具有低栅极电阻、降低高漏源电压VDS时的导通电阻RDS-ON等优势,且相比采用欧姆接触的P-GaN结构,此结构降低了栅极漏电流。 凹槽栅结构 凹槽栅结构如图所示,此结构通过电感耦合等离子体(Inductively Couple Plasma,ICP)干法刻蚀技术刻蚀掉栅极下方区域一定厚度的AlGaN势垒层,当AlGaN势垒层厚度减薄到一定程度时,沟道内的2DEG浓度会足够低。凹型栅极下方的整个AlGaN势垒层被去除,栅极下的2DEG消失,栅极金属下沉积了Al2O3膜作为栅极电介质,可防止由于器件尺寸越来越小而引发严重栅极漏电流、击穿电压过低等问题。在零栅压下,2DEG浓度小到可以忽略,器件处于关断状态。只有施加正栅压后,导电通道才会恢复,实现器件导通,即实现增强型特性。但除去栅极下方的势垒层,AlGaN势垒层其他区域的未被减薄,2DEG浓度保持原有水平。因此,凹槽栅技术制成的GaN FET在饱和电流和跨导方面较有优势。 Cascode结构 Cascode结构是由高压耗尽型GaN HEMT和低压增强型Si MOSFET(金属氧化物半导体场效应晶体管)级联构成的,如图5所示。   从结构可知,当器件不加栅压且漏源电压大于零时,工作在正向阻断模态;当栅压大于Si MOSFET的阈值电压时,器件正向导通;一旦Si MOSFET反向导通,器件将工作在反向导通模态。又因为Si MOSFET的漏源电压Vds_Si给GaN HEMT的栅源电压Vgs_GaN提供负偏置电压,因此控制Si MOSFET的通断即可控制GaN HEMT的通断。当然,这种结构由于引入了硅基器件,因此对封装的要求较高,体积也较大。 与其他结构GaNFET相比,Cascode GaNFET的结构,电压等级较高、驱动电压范围较宽,但对dv/dt和di/dt敏感,特别是在高频时,共源电感过大可能会使器件损坏。Andrew等人通过将智能栅极驱动与Si MOSFET集成,驱动耗尽型GaN HEMT,形成智能Cascade GaNFET。该智能Cascade GaNFET内置电流检测、可调输出电阻、可调电流检测率和智能数字控制。实验表明,此改进的Cascode结构通过利用动态开关技术,可以减少栅极振荡、降低高电压和电流转换速率、解决dv/dt和di/dt问题,优化EMI。 GaN FET参数   GaN FET外形   MOSFET VS GaNFET对比      参考文档: 《 氮化镓FET(HEMT)》——Transphrom 《氮化镓功率器件基础培训》北高智 工业电子事业部 邱勉为 《GaN FET的结构、驱动及应用综述》2020年电子技术应用第1期 伍文俊,兰雪梅 |